During an investigation into a software performance problem an engineer doubles the clock frequency of a cached ARM processor running the software. Unfortunately the performance of the application does not increase by very much, despite running on the processor for 100% of the time. What is likely to be the main bottleneck in the system?

Which of the following is TRUE for dynamically linked executables?

Which of the following is an external exception?

An advantage of removable flash memory over built-in flash memory is that:

An ARM processor connected to a Generic Interrupt Controller (GIC) is handling an active interrupt 11. A new interrupt 12 that is received at the GIC is forwarded to the processor, and the active interrupt 11 is preempted. Which of the following possible values of 11's priority (P1), 12's priority (P2) and the processor’s priority mask (PM) permit this to happen? Assume there are 256 priority levels implemented.

Assume a multicore processor with coherency management based on the MESI protocol. When a core changes the contents of a shared cache line, what is the final status of that line in the local cache?

Under which of the following circumstances would a DSB instruction be used?

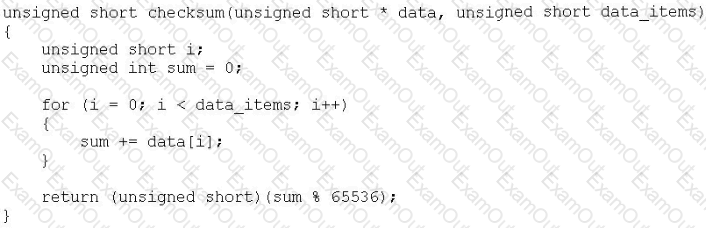

In an ARMv7-A system, the following C function calculates a simple checksum for an input data packet of variable length. The checksum is defined to be the sum of all of the 16-bit data items in the packet modulo 65536. The parameter data_items contains the number of 2-byte data items in the packet, and it cannot be zero by design.

When using an ARM compiler, which TWO of the following optimizations could improve the performance of this code? (Choose two)

When debugging an embedded Linux system, which one of the following techniques can be used to halt a single user thread, while allowing other threads to continue to run during the debug process?

The Cortex-A9 processor has 6 breakpoint units and 4 watchpoint units. What is the maximum number of breakpoints the debugger can set on code in ROM?