If the memory location 0x5000 contains 0Xffff0001, what is the value of r0 after the following instructions are executed?

MOV r1, #0x5000

LDRSH r0, [r1]

ADD r0, r0, #1

(Assume a little-endian memory system)

When using an Operating System, which of the following operations can NOT typically be done by user processes?

A Programmer's View CPU model usually provides:

In an operating system environment, most applications are executed in which processor mode?

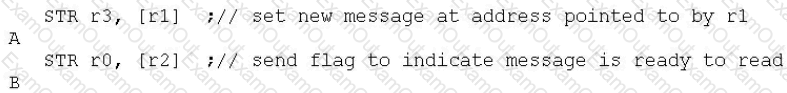

A message passing system between two CPUs is implemented using data stored in a shared area of memory. To pass a message, the first CPU executes the instructions:

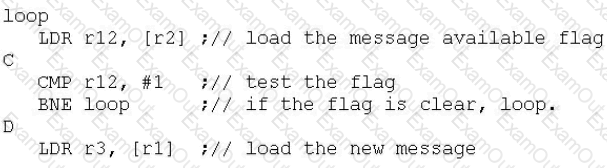

The second CPU receives the message using the instructions:

On both CPUs, r1 = 0x5000 and r2 = 0x6000. At which of the points A, B, C and D must Data Memory Barrier (DMB) instructions be placed in order to ensure messages are passed reliably and efficiently?

What is an "Entry point" in an application?

On an ARM processor that does not implement Security Extensions, which one of the following can be the starting address of the exception vector table?

What side-effect could using a debugger to read memory contents have?

A standard performance benchmark is being run on a single core ARM v7-A processor. The performance results reported are significantly lower than expected. Which of the following options is a possible explanation?

In a Cortex-A9 processor, when the Memory Management Unit (MMU) is disabled, which of the following statements is TRUE? (VA is the virtual address and PA is the physical address)